ET Pathfinder Timing¶

Project description¶

This wiki page contains information about the Einstein Telescope Pathfinder timing system.

A prototype system for Virgo and ET Pathfinder evaluation is built based on SPEC7 and an external Low Phase Noise oscillator. The SPEC7 connects to a Grand-Master White Rabbit timing source. SPEC7 creates a copy (TIA) of the Grand Master absolute time and uses this to generate an IRIG-B signal. The phase of the 125 MHz WR clock output (WR Clk Out: J20/J21) is phase aligned with the Grand Master.

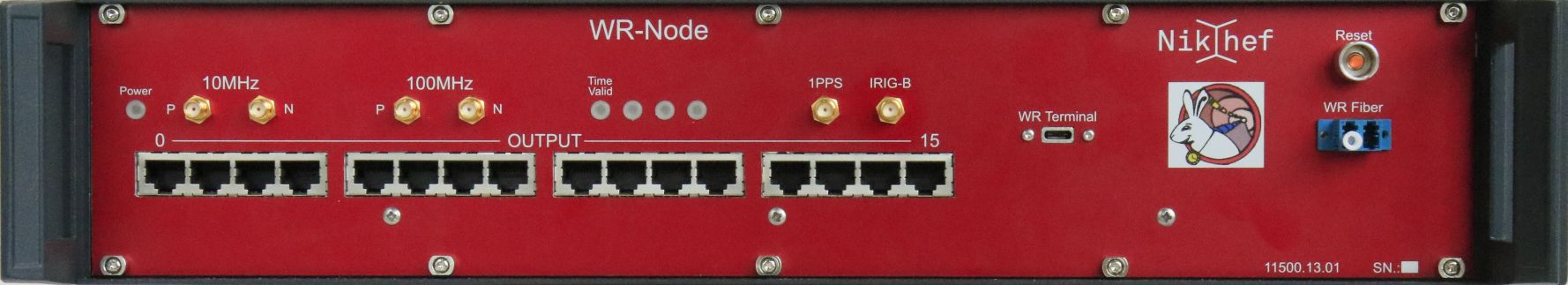

Figure 1 shows a picture of the Virgo Demonstrator WR-node front panel.

Figure 1: Virgo Demonstrator WR-node front panel.

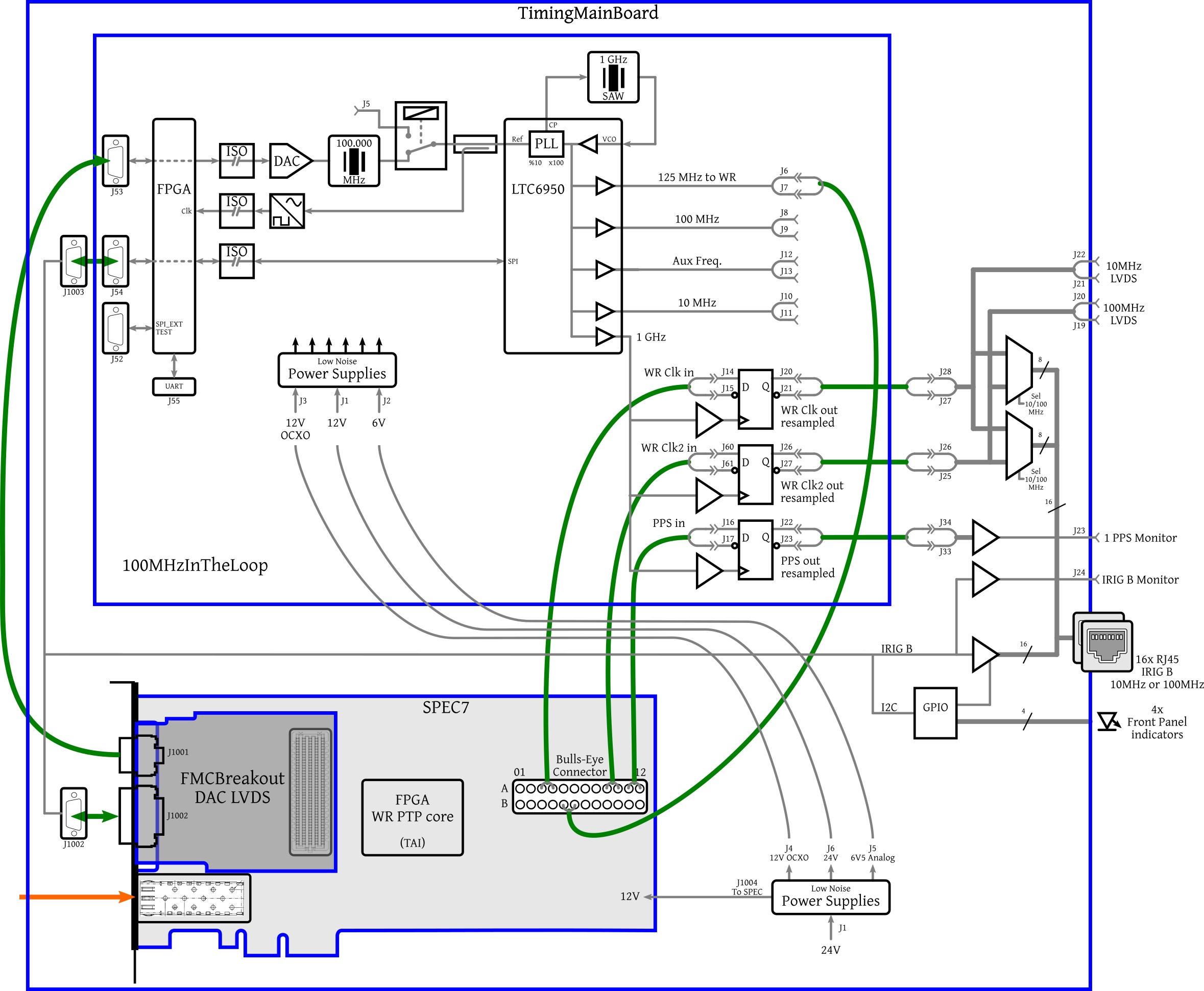

Both SPEC7 and the Low Phase Noise oscillator Printed Circuit Board are connected to a Timing Main Board that interfaces the 10/100 MHz Clock and IRIG-B signals to sixteen RJ45 connectors according to the standard that is currently used on the DAQ-boxes at Virgo. By doing so, the complete assembly is a direct drop in replacement for the current timing system at Virgo.

An FMC Breakout is plugged on the SPEC7. This board drives the DAC (LVDS) signals that connect to the DAC/VCXO on the Low Phase Noise oscillator board and feeds the IRIG-B signals to the Timing Main Board.

The Timing Main Board acts as a 16 channel fan-out for the 10 MHz and 100 MHz clock signals that are generated by the Low Phase Noise oscillator PSB and the IRIG-B time signals.

Project information¶

Figure 2 shows an overview of the system that is composed out of several subsystem Printed Circuit Boards (PCBs).

Each subsystem PCB is bounded by a blue line.

Several connections (shown in green) are made by (RF) cables between the sub-system boards.

Figure 2: Block diagram overview of the timing system. The various subsystem PCBs are bounded by blue lines.

- SPEC7

- FMCBreakout_extended

- 100MHzInTheLoop: Low Phase Noise External Oscillator

- TimingMainBoard: Timing Main Board for timing signal fan-out

Figure 3 shows the interior of the Virgo Demonstrator WR-node.

Figure 3: Virgo Demonstrator WR-node internal.

- Future developments

- BabyWR: General purpose small plugable WR node

- Frequently Asked Questions

Other info (not directly related to timing)¶

Contacts¶

General questions about project¶

- Guido Visser -Nikhef

- Peter Jansweijer - Nikhef

Status¶

| Date | Event |

|---|---|

| 29-09-2020 | Initial Meeting with LAPP. |

| 17-03-2021 | Start working on project. Collecting main specifications. |

| 26-04-2021 | FMCBreakout_extended ready for production. |

| 15-10-2021 | 100 MHz In The Loop ready for production. |

| 18-10-2021 | Start layout Timing Main Board. |

| 09-02-2022 | Morion Oscillators and 100MHzInTheLoop Board arrived; added link to future BabyWR page. |

| 01-03-2022 | Timing Main Board arrived. |

| 10-06-2022 | Added pictures. |

26 February 2024