Various FPGA Phase Noise Performance¶

Various FPGA families behave different with respect to phase noise.

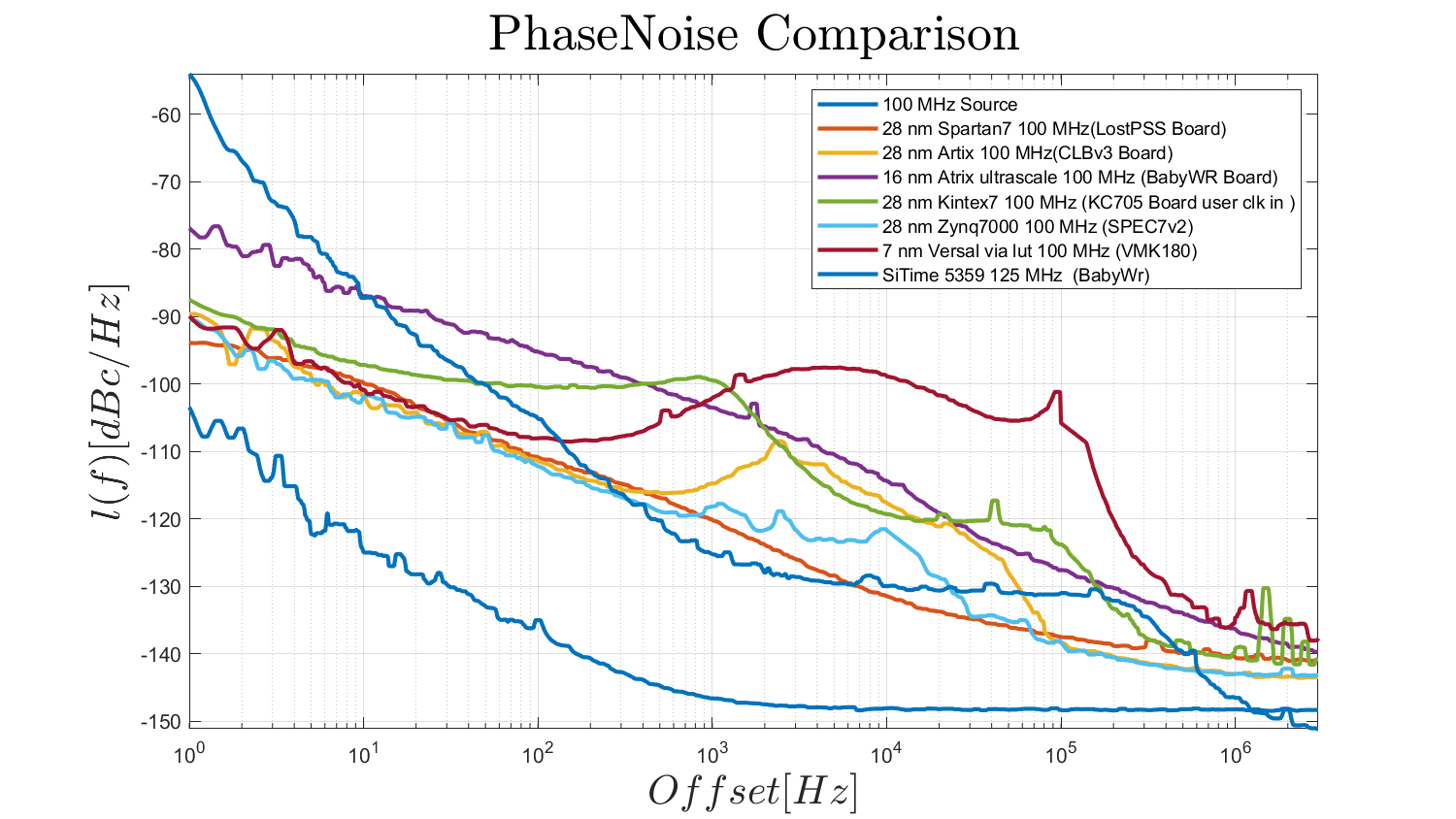

The Artix Ultrascale+ FPGA uses a 16nm FinFET process in contrast to the 28 nm 7-Series FPGAs. It is expected that Phase Noise will increase when transistor sizes (node size) decrease ([Claudio E. Calosso and Enrico Rubiola, Phase Noise and Jitter in Digital Electronics). Therefore it was decided to measure and compare several FPGAs. The measurement results can be found in Figure 1.

Figure 1: Phase Noise Comparison between FPGAs.

Except for the 100MHz clock source and the 125 MHz* and the SiTime5359 plot, Figure 1 compares different FPGAs with different transistor sizes:

- 28nm (Spartan7, Artix7, Kintex7, Zynq7000)

- 16nm FinFET (Artix Ultrascale+)

- 7nm FinFET (Versal)

All measured Xilinx FPGAs contain a simple LVDS IBUF => OBUF design that is clocked with the 100 MHz clock source.

The 28nm devices show equal 1/f noise while the 16nm Artix Ultrascale+ plot is significantly worse.

The SiTime5359 plot shows the free running 125 MHz reference oscillator on the BabyWR+BabyWR-Carrier board (same devices as used for the Artix Ultrascale+ measurement). This plot meets the performance specifications of the SiTime devices.

The bumps (in the range 100 Hz and 300 KHz) in the plots for Artix7, Kintex7 and Versal are probably due to FPGA "System Monitor" and JTAG circuitry and/or output regulation of the switched mode power supplies that are part of the evaluation platforms that were used for the measurements. However the 1/f phase noise trends are visible.

*) to compare 125MHz with 100MHz one should subtract 20log(125/100) ~ 1.9 dB

General questions

- Guido Visser -Nikhef

- Peter Jansweijer - Nikhef

26 February 2024