100 MHz In The Loop V2.0¶

Project description¶

General¶

Only one V2.0 board is ever produced! By accident the solder mask was green instead of red and the silkscreen was forgotten.

This board had issues with the DAC granularity; see below.

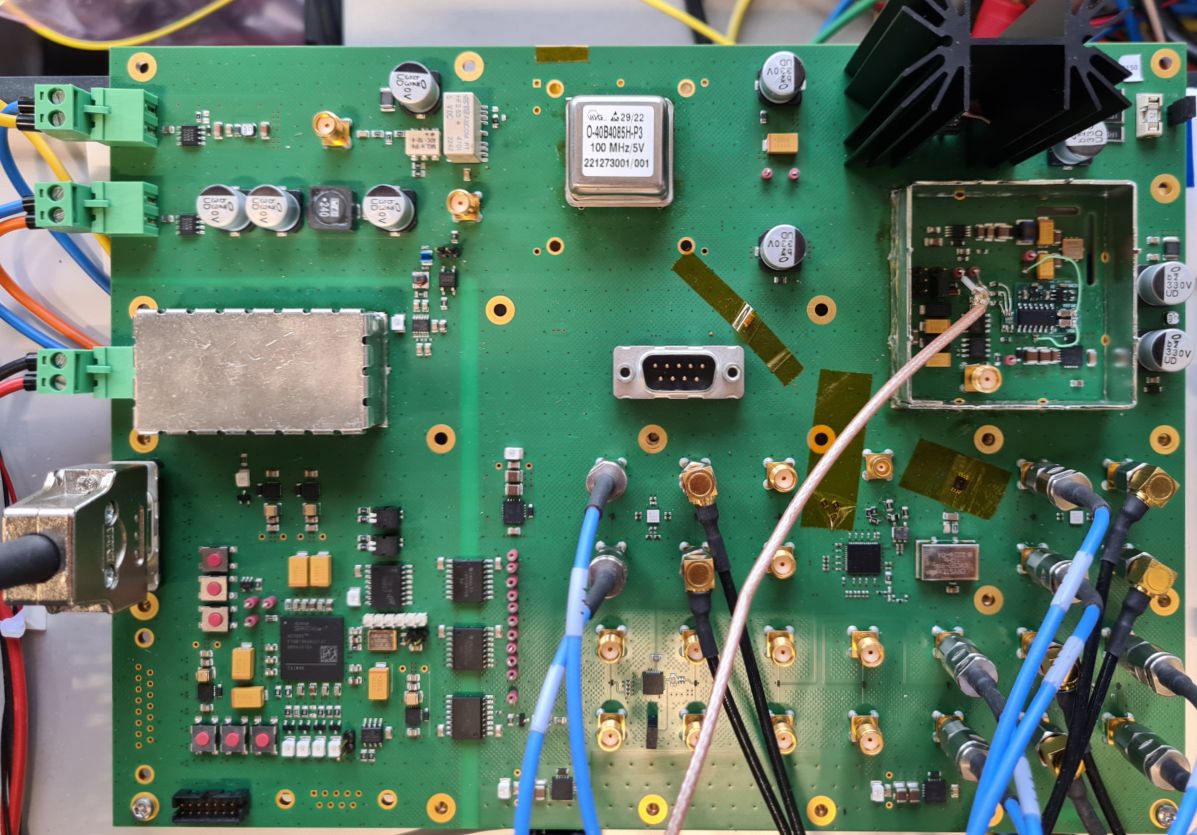

Figure 1 shows a preliminary picture of the 100MHzInTheLoop PCB.

Figure 1: Picture of the 100MHzInTheLoop PCB V2.0

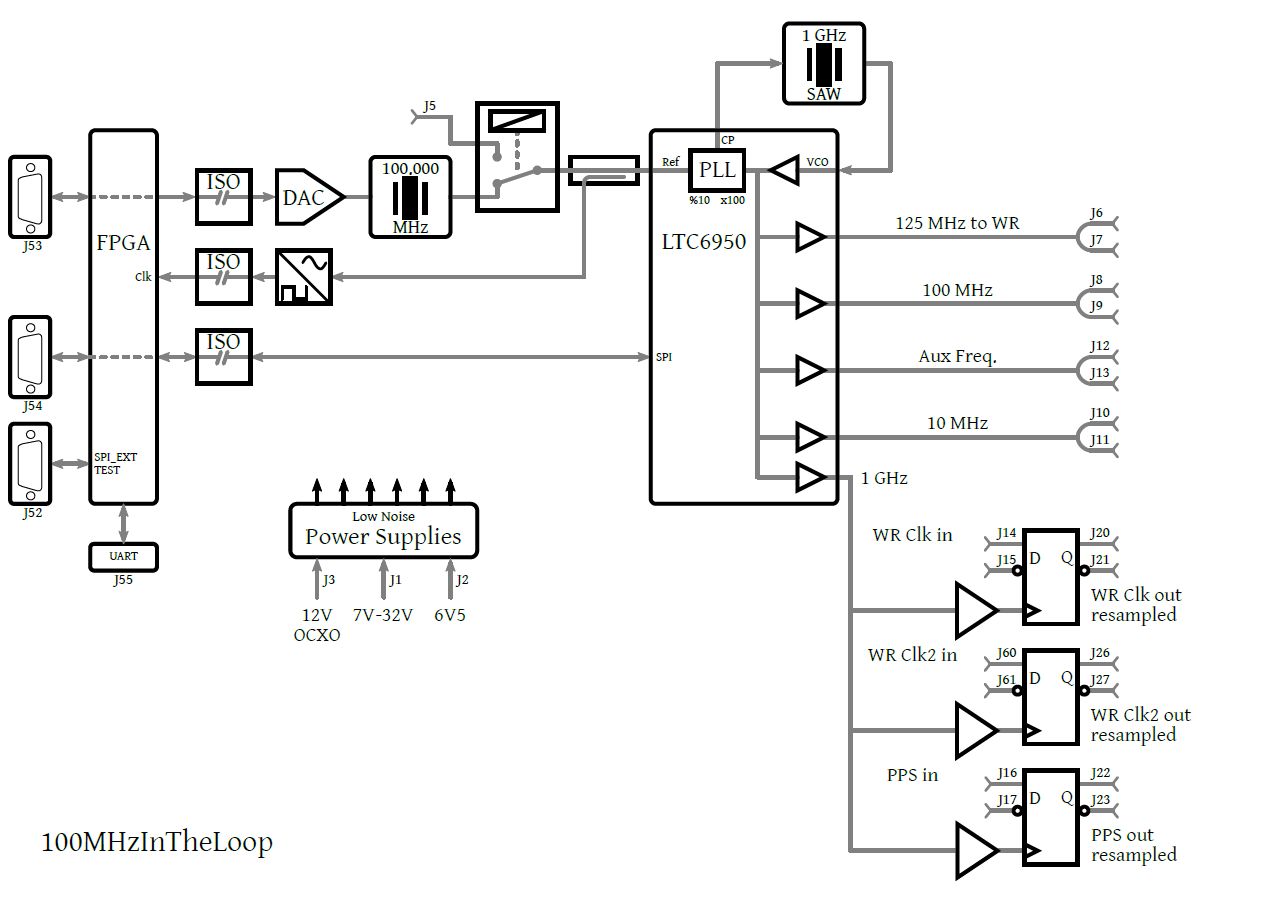

Figure 2 shows a block diagram of the 100MHzInTheLoop board.

Figure 2: A Block diagram of the 100MHzInTheLoop board

This Board contains a 100 MHz high precision low phase noise OCXO. The oscillator can be used as an external high precision oscillator for White Rabbit (WR) applications that need to generate low phase noise clocks.

The OCXO can be tuned via a DAC. The 100 MHz output of the oscillator is the reference for a PLL (LTC6950) that has a low phase noise 1 GHz Surface Wave Acoustic (SAW) VCO.

The PLL needs initialization via SPI. Therefore the SPI bus is connected to a Spartan-7 FPGA such that the firmware implementation of this FPGA can either feed forward an external SPI bus or drive the SPI bus stand alone via a MicroBlaze implementation.

The PLL generates a 125 MHz clock that is used as WR reference clock. It can also generate 10 and 100 MHz clock that are used in the Virgo demonstrator and ET-Pathfinder. An auxiliary frequency can be generated as well.

DAC Granularity¶

It was found that the 16 bit DAC granularity using a KVG oscillator (O-40-ULPN-100M) with wider Pull Range was not sufficient. For the KVG it calculates 7.6 mHz / DAC-bit (@16 bits).

The Morion MV137 of 100MHzInTheLoop V1.0 had a 1.5 mHz / DAC-bit (@16 bits) which is 5 times better. Increasing the DAC granularity with 4 bits to a 20 bit DAC gives a 16 times better sensitivity. Therefor the design was enhances to contain a 20 bit DAC, leading to 100MHzInTheLoop V3.0

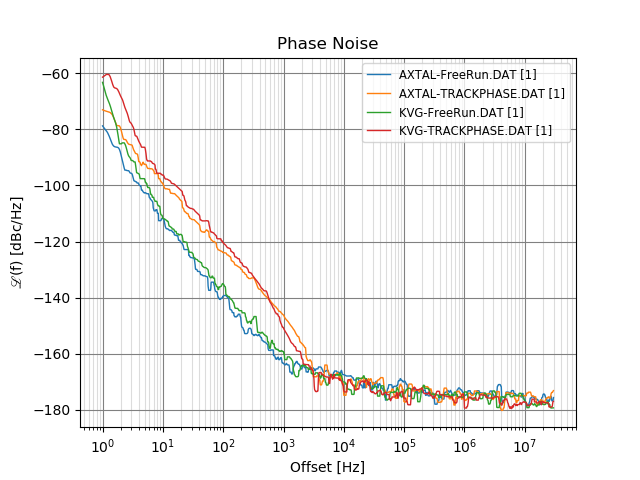

Insufficient DAC granularity gave an increase in phase noise below 3 KHz (which is the SoftPLL update rate) as can be seen in Figure 3.

Figure 3: Added Phase Noise in TRACK-PHASE when using KVG or AXTAL with insufficient DAC granularity.

Design details¶

- Schematics (Note: Design created with Mentor Graphics using a Xpedition).

- Manufacturing files 11500.04.02 100MHzInTheLoop (Note: Design created with Mentor Graphics using a Xpedition).

- Repository containing firmware/software implementation for Spartan-7 MicroBlaze"

- Change log towards V3.0

Older versions¶

Contacts¶

General questions about project¶

- Guido Visser -Nikhef

- Peter Jansweijer - Nikhef

Status¶

| Date | Event |

|---|---|

| 15-01-2024 | separate page for 100MHzInTheLoop to V2.0. |

15 January 2024